42 Tabel Kebenaran Counter Sinkron Terlengkap

Detail Gambar Tabel Kebenaran Lengkap Koleksi Nomer 35

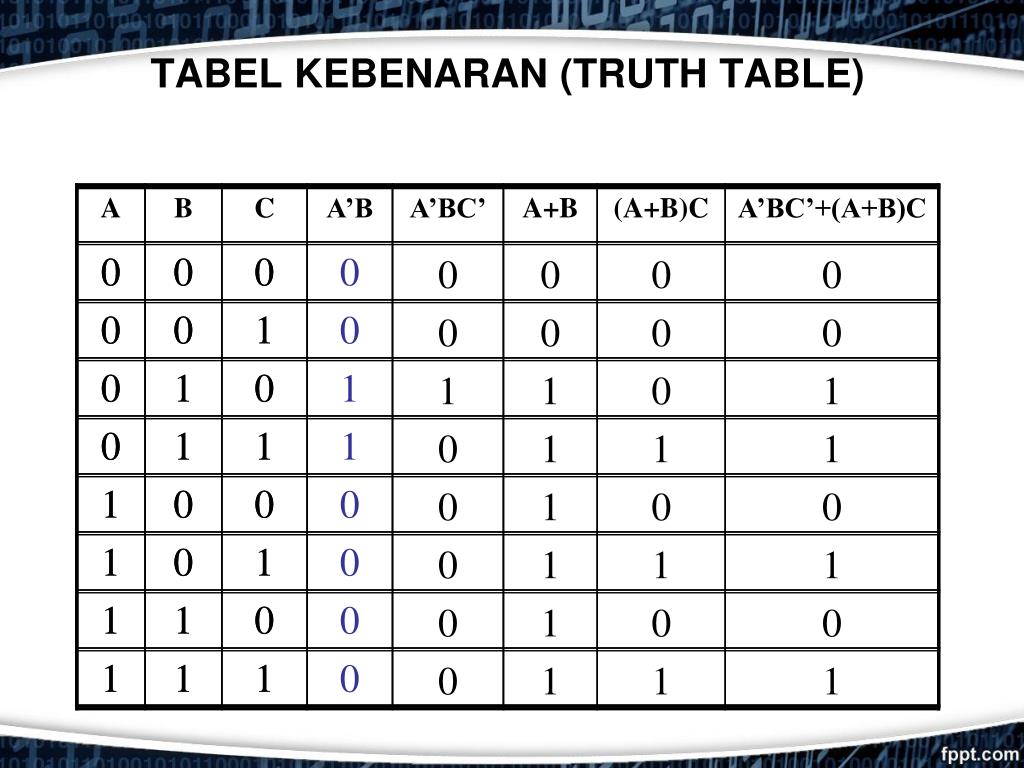

Dengan demikian kondisi akhir dari keluaran DCBA= 0100. Tabel 1. Tabel Kebenaran Asynchronous Counter Biner 4-bit Pada proses kerjanya, salah satu kelemahan pencacah asinkron adalah waktu penundaan propagasi (Propagasi Delay) flip-flop yang diakumulasi yang akan menghasilkan jumlah output yang salah.

Tugas gambar counter 4 bit, clock map dan tabel kebenaran

perhatikan gambar Jenis pencacah counter asinkron ini dihitung ke atas pada setiap tepi trailing sinyal clock input mulai dari 0000. Tabel Kebenaran Counter Decade.. katakanlah 262.144kHz dan pencacah (counter) riak 18-bit (Modulo-18), kita dapat dengan mudah membuat sinyal timing 1Hz presisi seperti yang ditunjukkan di bawah ini. Sinyal.

Rangkaian, Cara Kerja dan Tabel Kebenaran Multiplexer dan Demultiplexer YouTube

Tabel Kebenaran dari Up Counter Asinkron 3-bit Gambar rangkaian Up Counter Asinkron 3 bit : 5 Timing Diagram untuk Up Counter Asinkron 3 bit : Berdasarkan bentuk timing diagram di atas, output dari flip-flop C menjadi clock dari flip-flop B, sedangkan output dari flip-flop B menjadi clock dari flip-flop A. Perubahan pada negatif edge di masing.

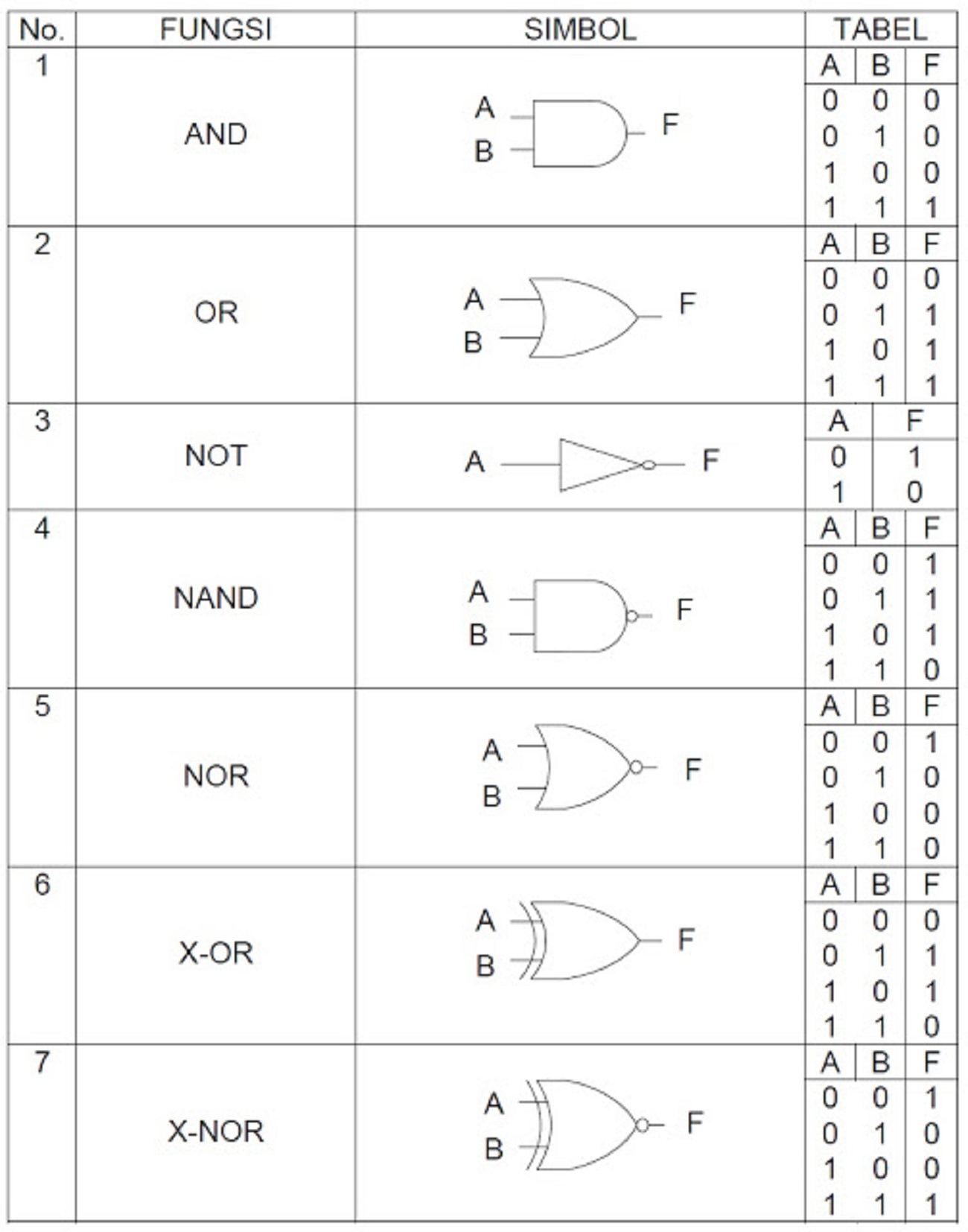

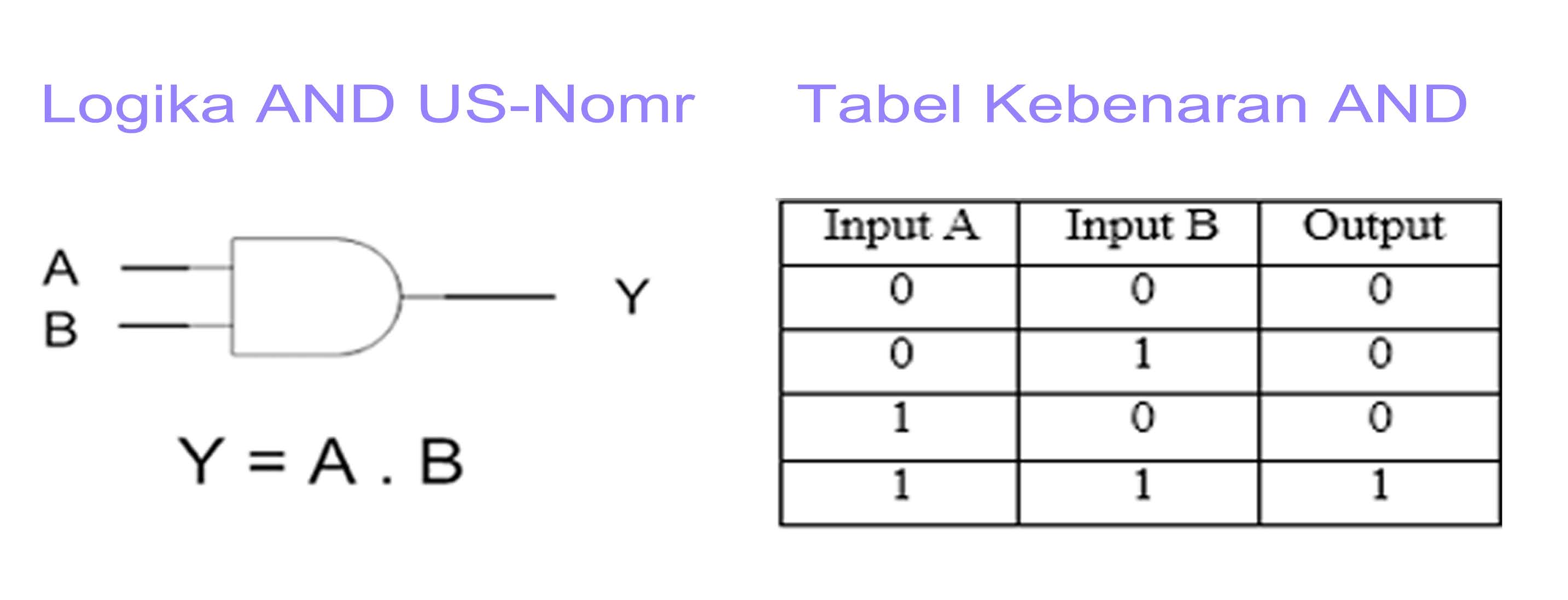

kuningn TABEL KEBENARAN AND OR NOT

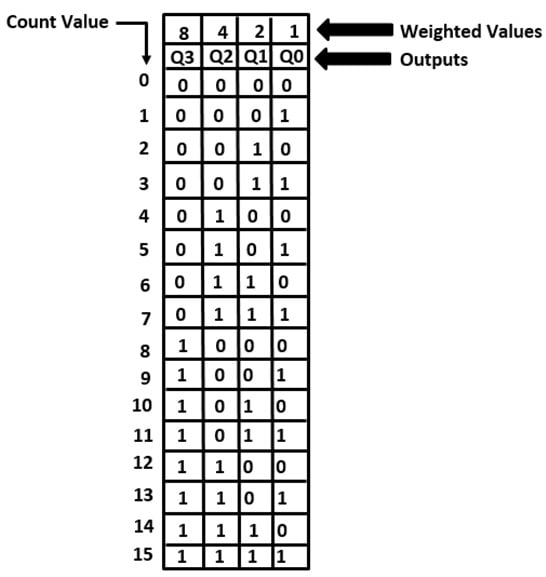

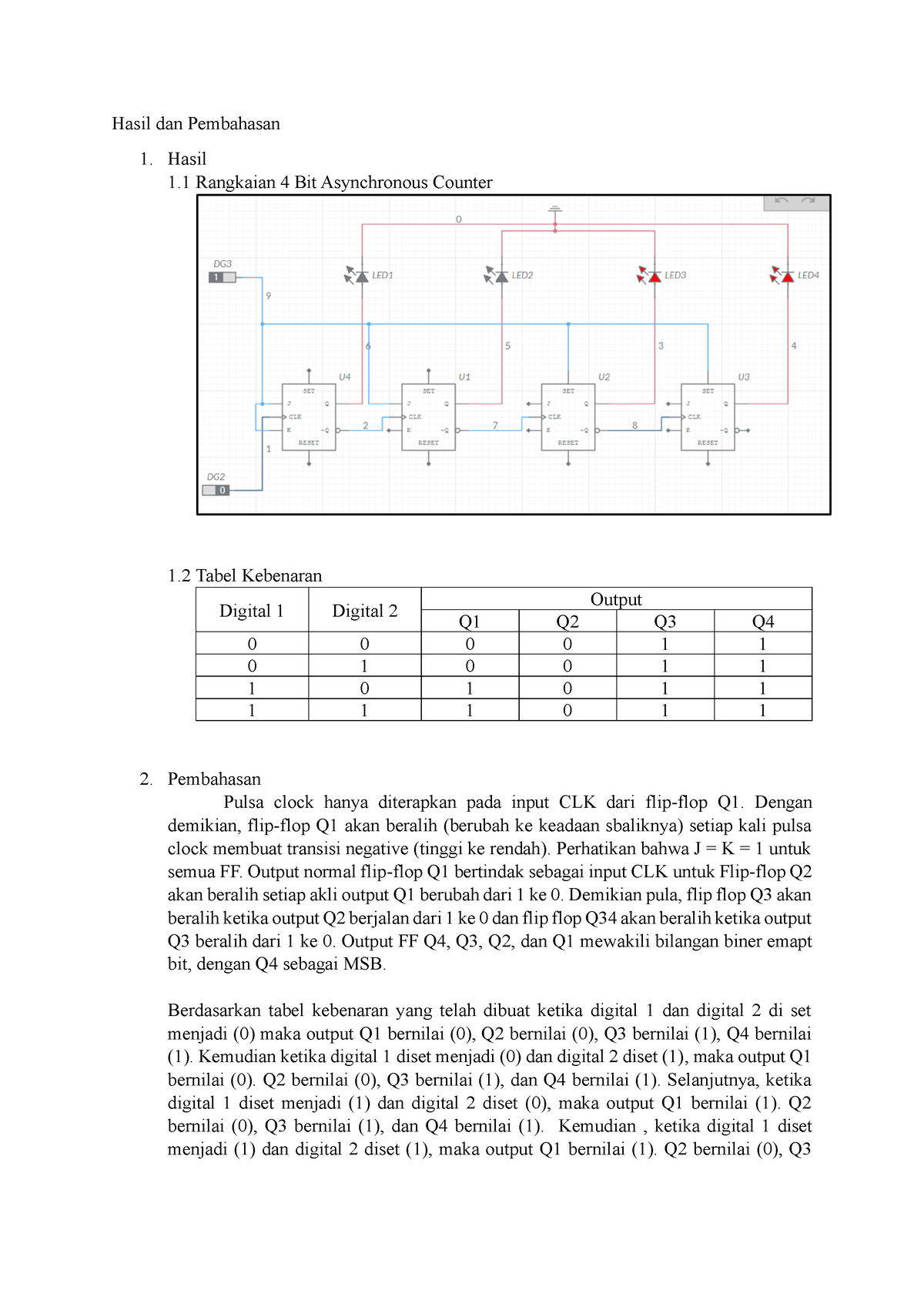

Output FF Q4, Q3, Q2, dan Q1 mewakili bilangan biner emapt bit, dengan Q4 sebagai MSB. Berdasarkan tabel kebenaran yang telah dibuat ketika digital 1 dan digital 2 di set menjadi (0) maka output Q1 bernilai (0), Q2 bernilai (0), Q3 bernilai (1), Q4 bernilai (1).

Tabel Kebenaran 4 Bit My XXX Hot Girl

Membuat rangkaian register 4 bit menggunakan selain D flip-flop. 4. Membuat rangkaian register serial in parallel out dan tabel kebenarannya. 5.3. HASIL PERCOBAAN 1. Hasil percobaan permasalahan pertama. a. Rangkaian logika pada Gambar 5.1 merupakan rangkaian counter up sinkron. b. Membuat tabel kebenaran berdasarkan hasil simulasi. Tabel 5.1.

05 cara kerja dan tabel kebenaran Multiplexer dan Demultiplexer YouTube

Laporan Counter Asinkron laporan praktikum teknik digital disusun oleh nama ammar arrafi wahyu saputra nim 22537144019 kelas j2 prodi teknologi informasi

Contoh Soal Gerbang Logika Dan Tabel Kebenaran LEMBAR EDU

Kami dapat menunjukkan secara visual pengoperasian pencacah (counter) Asinkron 2-bit ini menggunakan tabel kebenaran dan diagram keadaan. Diagram Keadaan dan Pencacah Counter MOD-4 Kita dapat melihat dari tabel kebenaran pencacah, dan dengan membaca nilai-nilai QA dan QB, ketika QA = 0 dan QB = 0, hitungannya adalah 00.

Detail Gambar Tabel Kebenaran Lengkap Koleksi Nomer 24

Gambar 4.1 Rangkaian untuk Percobaan Synchronous Counter 74LS190 2. Ukur catu daya DC sebesar +5V.. Tabel 4.1 Data Hasil Percobaan IC 74LS190 MASUKAN LUARAN. 1. Buatlah rangkaian Synchronous Counter Up 4 bit dengan Flip-Flop JK (dengan table kebenaran) Bit Selector D3 (8) D2 (4) D1 (2) D0 (1)

4 Bit Binary Counter Truth Table

Gambar rangkaian Up Counter Sinkron 3 bit Gambar rangkaian Down Counter Sinkron 3 bit Rangkaian Up/Down Counter Sinkron Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down Counter. Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya input eksternal sebagai control yang menentukan saat menghitung Up atau.

4 Bit Asinkron Counter Hasil dan Pembahasan Hasil 1 Rangkaian 4 Bit Asynchronous Counter 1

Rangkaian Up/Down Counter Asinkron 3 bit. 5.4. PROSEDUR PERCOBAAN. Pada Modul Trainer ITF-02, buatlah rangkaian Up Counter Asinkron 3 bit seperti gambar 5.1. Jalankan Counter tersebut selama 15 clock, dan buatlah Tabel Pengamatannya. Jalankan Counter tersebut selama 20 clock, dan buatlah Tabel Pengamatannya.

Gambar Tabel Kebenaran Lengkap

Rangkaian Up/Down Counter 4 Bit. Rangkaian up/down counter diatas merupakan counter synchronous 4 bit yang disusun dengan JK-FF. Proses hitung naik (count up) akan terjadi apabila jalur input Up/Down diberikan logika HIGH dan akan melakukan hitung mundur (count down) apabila jalur input up/down tersebut diberikan input LOW.

42 Tabel Kebenaran Counter Sinkron Terlengkap

Sistem Digital ( Rangkaian Counter). [PowerPoint slides]. Literature Penerapan Rangkaian Pencacah Digital Flip-flop merupakan rangkaian digital yang digunakan untuk menyimpan satu bit secara semi.

Penjelasan Lengkap Gerbang Logika Dan Tabel Kebenaran Unamed

Rangkaian Prioritas Encoder. Rangkaian Encoder mengambil semua input data mereka satu per satu dan mengubahnya menjadi kode biner yang setara pada outputnya. Tidak seperti multiplexer yang memilih satu jalur input data individu dan kemudian mengirimkan data itu ke jalur output tunggal atau switch, Digital Encoder lebih sering disebut Encoder.

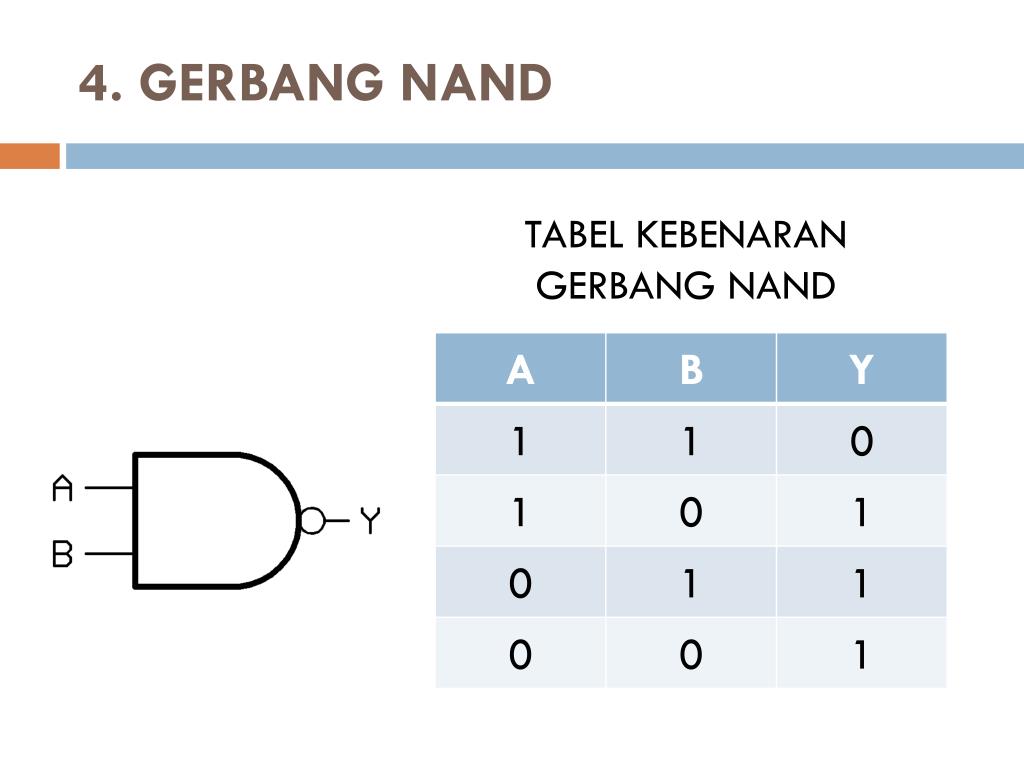

Tabel Kebenaran Nand Ruang Ilmu

Counter MOD menggunakan 4 FF menggunakan tambahan gerbang-gerbang eksternal 2n Cara 1: Mode Toggle • Buat input-input j dan k setiap flip-flop bernilai 1 • Gunakan tabel kebenaran untuk menentukan hitungannya. • Jika counter mencapai nilai bilangan, harus di-reset ke nilai 0 • Dengan gerbang-gerbang logika, masukkan input dari flip-flop.

Contoh Soal Gerbang Logika Dan Tabel Kebenaran Berbagi Informasi Bermanfaat

Gambar 1. Pencacah biner asinkron 4-bit. Bila keluaran suatu flip-flop memicu flip-flop lainnya, pencacah tersebut disebut pencacah kerut (ripple counter) atau pencacah tak serempak (asinkron); flip-flop A harus berubah keadaan sebelum dia memicu flip-flop B; B harus berubah sebelum dia dapat memicu C; dan seterusnya.

Arithmetic Logic Unit Half adder, Full Adder dan Parallel Adder » Folderku

Rangkaian shift register 4 bit Gambar 2. Tabel kebenaran dan timing diagram shift register 4 bit . Ring Counter. Rangkaian Ring Counter dengan IC 4017 Gambar 5. Tabel kebenaran dan timing diagram ring counter dengan IC 4017 . Johnson counter Gambar 6. Johnson counter Gambar 7. Johnson Counter dengan IC 74164 Gambar 8. Tabel kebenaran dan.